開発の特長

- 独自の電界緩和構造により、素子の信頼性を確保

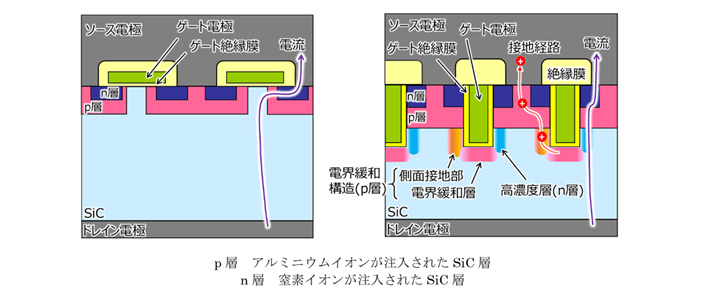

- 独自の電界緩和構造により、トレンチ構造で、1500V以上の耐圧性能を保持しながら、電界強度を従来のプレーナー型構造並みに抑制し、素子の信頼性を確保

- 斜め方向からアルミニウムを注入することにより形成された側面接地部にて電界緩和層とソース電極を電気的に接続し、高速スイッチング動作を実現

- 局所的な高濃度層形成により、世界最高レベルの低抵抗化を実現

- 斜め方向から窒素を高濃度に注入することにより、より通電しやすい高濃度層を局所的に形成して電流経路の抵抗を低減

- 素子抵抗率を半減※6し、世界最高レベルの1cm2あたり1.84mΩ(ミリオーム)を実現

- 発熱の抑制により、パワーエレクトロニクス機器の省エネ化・小型化に貢献

- ※6

当社のプレーナー型SiC-MOSFETとの室温での比較において

今後の展開

パワー半導体素子のさらなる特性向上を図るとともに、長期信頼性評価を進め、2021年度以降の実用化を目指します。