開発NOTE

製品開発に加え、次の基本技術を開発することが我々のミッションです。

先端技術総合研究所

先端技術総合研究所

田中 梨菜

三浦 成久

田中 貴規

我々の研究開発は大きく2方向に分かれます。ひとつは新製品のための開発です。ルームエアコンのケースでは、省エネ性向上の切り札として、既存のSiパワーデバイスをSiCに切り替えたいという製作現場からの強い声に対し、ウェハからチップ製造までの開発を担当しました。

パワーデバイスのみを製造している企業では、汎用性や大量生産のしやすさなどが開発の重要ポイントになります。それに対して、当社の特徴は、製品設計の現場と研究所が直接リンクしているという点にあります。

現場の要望や個々の製品に合わせて、より最適なパワーデバイスを開発することが可能です。

そしてもうひとつの我々の重要なミッションは、今後の当社のデバイス事業を支える“次世代技術の開発”と“基礎技術の強化”に取り組むことです。その一例として、トレンチ型のSiC-MOSFET※2や化学気相成長法(CVD法)によるSiCのエピタキシャル成長などの技術があります。

次世代「トレンチ型MOSFET」の実用化にとって、大きな一歩となる技術だと自負しています。

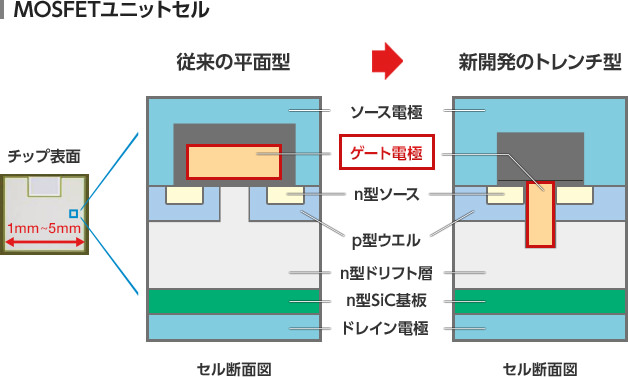

MOSFETとは、ゲート電極に加える電圧を制御し、ソース電極とドレイン電極間の電流の流れをON/OFFするパワーデバイスの一種です。

従来の構造は平面型と呼ばれ、ゲート電極を横に配置します。現在、我々が開発に挑んでいるのは次世代のトレンチ型SiC-MOSFETです。このトレンチ型はゲート電極をSiCの内部に縦に埋め込む構造で、電力損失が少なく省エネ性が高い、デバイスを小型化できるなど、さまざまな利点がある反面、非常に難しい技術を必要とします。

特に高い電圧がかかった時に素子が壊れやすいという問題があり、実用化の大きな壁となっていました。この弱点を克服するために、我々はゲート電極下に保護層を設置し、これを電気的に接地する電極の配置を見直すなど、革新的な構造を開発しました。本技術により、製品化に向けて大きな一歩を踏み出したと考えています。

この研究はパワーデバイスに関する権威ある国際学会「ISPSD※3 2014」において、最も優れた若手研究者に贈られる「シャリタット・アワード」を受賞しました。これは、当社として、初めてであり、とても名誉に思います。

今回の受賞は、デバイス性能だけに力点を置くのではなく、デバイスの一番大事なところとも言える信頼性を製品化できるレベルまで高めたという、新しい着眼点でのデバイス設計をご評価いただき、受賞後も各方面から大きな反響がありました。

デバイスの性能と信頼性をいかに両立するかが、大きな課題でした。

田中 梨菜

田中 梨菜

ISPSD 2014

シャリタット・アワード受賞

パワーデバイスは裸眼では見えないほど小さな構造を作り込んで作製します。そこに流れる電流も同様、直接見ることはできないので、デバイスのなかで何が起きているか、シミュレーションで模擬し、設計・試作・評価を行っていきます。トレンチ型の開発で苦労した点は、信頼性を高めるための保護性能とデバイス性能をいかに両立するかということでした。

信頼性とひとことで言っても多くの項目があります。それらを広い範囲に目を配りながら、最適な構造を見つけるために日々研究を続けてきました。

パワーデバイスの研究開発は時間のかかる作業です。ひとつ素子を作るのにも半年近く必要なため、フィードバックされた試作の結果を得るためにはさらに半年かけなければなりません。よって、さまざまな状況を想定し、シミュレーションや試作品の解析を念入りに行い、盲点がないよう素子設計する必要があります。それでも熟慮とは裏腹にうまくいかず、悔しい思いをしたことは何度となくありました。しかし自分が設計し、思い通りの結果が得られた時の喜びは格別なものです。

SiCパワーデバイス開発の根底を支える技術、それがSiCエピタキシャル成長技術です。

田中 貴規

田中 貴規

次にSiCエピタキシャル成長技術についてです。

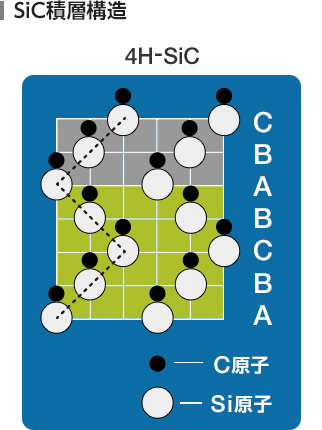

エピタキシャル成長技術とは、下地となる半導体基板の原子配列に合わせて新たな原子をその配列通りに積み上げてエピタキシャル膜を形成するプロセス技術です。SiCパワーデバイスは、SiC基板の上に、数マイクロメートルから数十マイクロメートルのSiCエピタキシャル膜を成長させ、そこにデバイス構造を作り込み、完成します。そのため、このエピタキシャル膜をいかに高品質なものに仕上げるかが、デバイス性能の向上にとって重要となります。

現状ではまだ、SiC基板の結晶性は完全とは言えず、基板中にはシリコン(Si)と炭素(C)原子間の結合の欠けやズレなどの結晶欠陥が存在しています。この結晶欠陥の一部は、エピタキシャル膜の原子配列に引き継がれると、デバイスの性能を低下させることが知られており、エピタキシャル成長によって、これらの有害な結晶欠陥を無害なものに変換する技術開発が求められています。

この分野についても、我々は確実に成果を上げており、学会発表などでも大変ご評価いただいています。SiCエピタキシャル成長技術はSiCデバイスにおける基礎技術であり、根幹を支える技術です。この技術の高度化がより信頼性の高い、高品質なSiCデバイスにつながります。

地道に実験を積み重ねていくことが、成功へのただ一つの方法です。

SiCエピタキシャル成長は化学気相成長法(CVD法)と呼ばれる手法を用いて行われます。

CVD法とは、高温加熱したSiC基板上に数種類の原料ガスを流し込み、熱エネルギーによる化学反応を利用して基板表面に膜を形成する手法です。研究では実際にCVD装置を使用し、成長と評価を繰り返しながら進めていきます。

同じ条件で実験をしたつもりでも異なる結果がでたり、これまで上手くできていたことが急にできなくなるなど、進捗が足踏みしてしまうこともしばしばあります。その原因のひとつひとつを丁寧に調査、解明し、品質改善を重ねていく毎日です。

原子が整然と一つ一つ並んでいく、そんなシーンを思い描きながら、原子と対話をするような気持ちで、結晶欠陥のないエピタキシャル膜の実現と、より信頼性の高いものづくりに向けて地道に研究を続けています。

それぞれの基礎研究がいつの日か融合し、社会に役立つチカラになるはずです。

トレンチ型SiC-MOSFETは、デバイス構造自体のポテンシャルを考えると、まだまだ伸びしろがあると思います。そこをどう伸ばしていくかが今後のテーマです。

固定概念に捕らわれることなく、柔軟にいろいろなアイデアを取り入れて、トレンチ型のみならず、さらには新しいデバイス構造にも挑戦していきたいと思っています。エピタキシャル成長技術については、結晶欠陥の密度をよりゼロに近づけることが大きな課題ですが、さらにその先としては、ますます複雑化・高度化するであろうデバイス構造にも対応できるエピタキシャル成長技術の研究にも取り組んでみたいと考えています。

トレンチ型デバイスの開発やエピタキシャル成長技術の強化など、高性能なデバイス構造と高品質なプロセス技術を組み合わせることが、真に競争力のある製品づくりにつながると信じています。自分の仕事の成果が世の中に出て、役に立っていると実感できる瞬間は、研究者にとって喜びあり、モチベーションのひとつです。

次や、次の次の社会に必要とされる製品を予見し、その実現に必要な基本要素技術の開発に勇気を持って挑戦する、そんな気概を持って、これからも研究開発に取り組んでいきます。

表彰実績

第48回 市村産業賞 功績賞を受賞

「3.3kV フルSiC 適用鉄道車両用推進制御装置」にて、第48回 市村産業賞 功績賞を受賞しました。

※2MOSFET:Metal Oxide Semiconductor Field Effect Transistor 金属酸化膜半導体電界効果トランジスター

※3ISPSD、International Symposium on Power Semiconductor Devices & ICs

※本開発の一部は国立研究開発法人 新エネルギー・産業技術総合開発機構(NEDO)の委託を受けて実施しました。