パワーエレクトロニクス機器の

さらなる省エネ化・小型化に貢献します。

概要

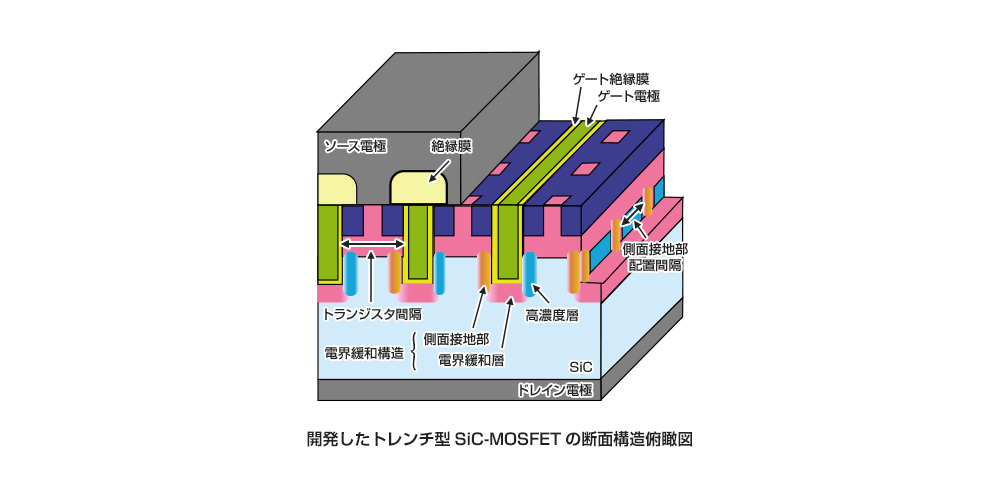

パワー半導体素子として、独自の電界緩和構造を採用したトレンチ型※1SiC※2MOSFET※3(MIT2-MOS:Multiple-Ion-Implantation into Tilted Trench Side Walls)を開発しました。

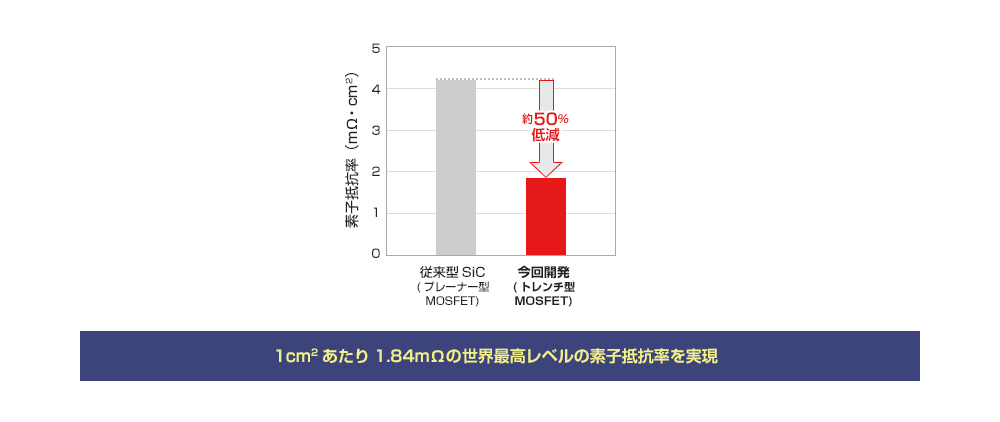

1500V以上の耐圧性能と1cm2あたり1.84mΩ(ミリオーム)という世界最高レベル※4の素子抵抗率※5の両立を実現。パワー半導体モジュールへの搭載で、パワーエレクトロニクス機器のさらなる省エネ化や小型化に貢献します。

技術ポイント

SiC-MOSFETはプレーナー型構造からトレンチ型構造へ

パワーエレクトロニクス機器では、さらなる省エネ化・小型化・高効率化のために、パワー半導体素子も電力損失がより少ないSiC-MOSFETへの切り替えが進んでいます。

SiC-MOSFETでは、素子抵抗率を下げるため、トランジスタセルの低抵抗化に加えてセルの高密度な配置が求められており、ゲート電極を半導体基板上に配置する従来のプレーナー型構造から、基板に溝(トレンチ)を形成してゲート電極を埋め込むトレンチ型構造へ変わりつつあります。トレンチ型にするとセル幅を狭めて高密度にセルを配置することができますが、プレーナー型と比べて、高い電圧をかけた時にゲート絶縁膜が破壊されやすいという課題がありました。

電界緩和構造の採用

高い電圧に耐えられるように、パワー半導体素子としての高信頼性を担保しながら、低抵抗な素子を実現したポイントは「独自の電界緩和構造の採用」「高濃度層の形成」「斜め注入の適用」です。

トレンチ底の角部は高い電圧がかかると強い電界が発生しやすく、ゲート絶縁膜が破壊されやすくなります。そこで、トレンチ底部に発生する強い電界からゲート絶縁膜を守る電界緩和層を設置。ゲート絶縁膜にかかる電界を従来のプレーナー型並みに抑制し、素子の信頼性を高めました。

さらにもうひとつは、電界緩和層に蓄積した電荷をソース電極に流し、スイッチング動作の速度を向上する側面接地部です。電界緩和層が電気的に絶縁されたままMOSFETでスイッチング動作を繰り返すと、電界緩和層に電荷が蓄積し、MOSFETが高速に動作できなくなり、スイッチング損失が増加してしまいます。

そこで、電界緩和層とソース電極をつなぐ側面接地部をトレンチの側面部に形成。高速なスイッチング動作が可能になり、スイッチング損失を低減できます。

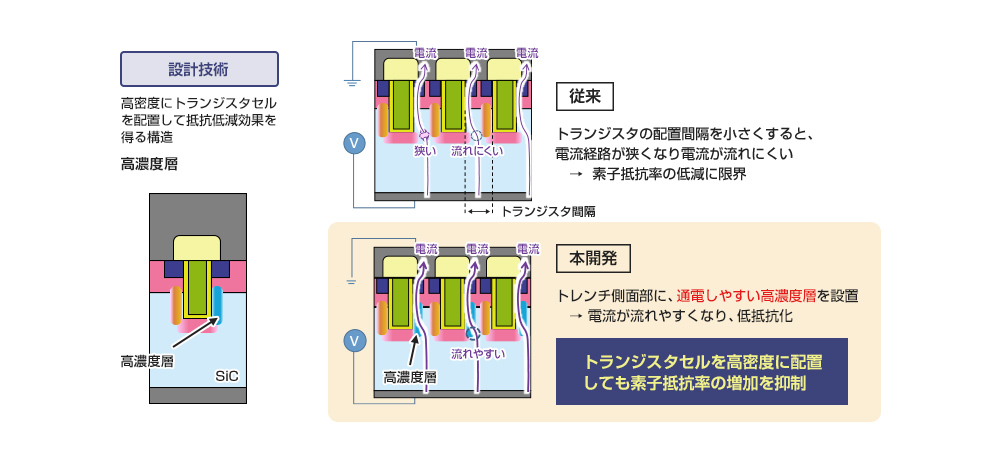

高濃度層の形成

トランジスタセルを高密度に配置すると多くの電流を流せますが、トランジスタの間隔を狭くしすぎると電流が流れにくくなり、素子抵抗率が増加します。

これを解決するため、トレンチ側面部に通電しやすい高濃度層を設置。高密度なトランジスタセルの配置において、高濃度層なしの場合と比べて素子抵抗率を約25%低減しました。

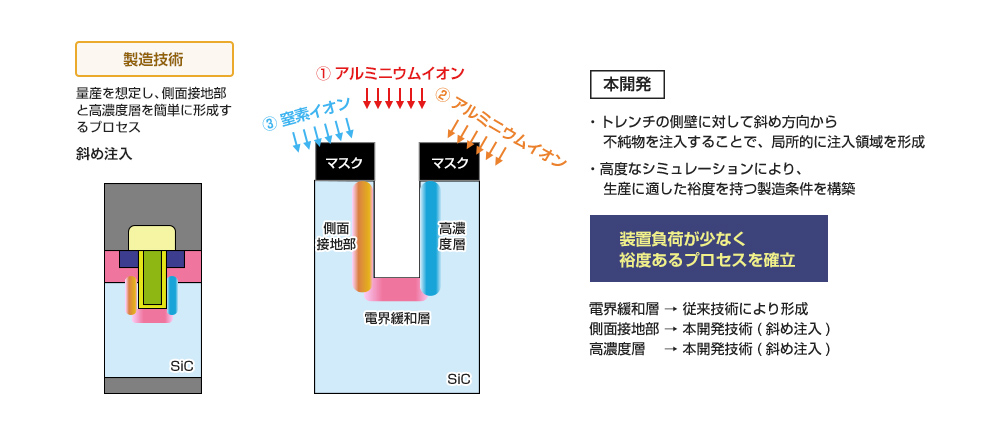

斜め注入の適用

従来のように垂直方向からではなく、トレンチの側壁に対して斜め方向からアルミニウムイオンや窒素イオンの不純物を注入。局所的な側面接地部と高濃度層を簡便に形成する手法を開発しました。

世界最高レベルの素子抵抗率を実現

電界緩和構造と高濃度層を局所的に配置した独自構造のトレンチ型SiC-MOSFETを開発。1500V以上の耐圧で、1cm2あたり1.84mΩという世界最高レベルの素子抵抗率を実現しました。

今後、パワー半導体素子としてさらなる特性向上を図り、長期信頼性評価を含め、実用化を目指した開発を進めます。

※1電圧をかけ電流の流れを制御するゲート電極を半導体基板に溝(トレンチ)の形で埋め込んだ構造。

※2Silicon Carbide (炭化ケイ素)

※3Metal Oxide Semiconductor Field Effect Transistor:金属酸化膜半導体電界効果トランジスタ

※4耐圧性能1500V以上の素子において。2019年9月30日現在、当社調べ。

※5素子面積1cm2の場合の室温における抵抗値、特性オン抵抗、単位 (mΩ・cm2)