三菱電機株式会社は、パワー半導体モジュールに搭載されるパワー半導体素子として、電流を高速に遮断する保護回路無しで使える、電力損失が世界最小※1のSiC※2パワー半導体素子を開発しました。パワーエレクトロニクス機器の高信頼性と省エネの実現に貢献します。

なお、本開発については、「ICSCRM 2017(The International Conference on Silicon Carbide and Related Materials)」(於:アメリカ Washington, D.C.、9月17日から開催) にて9月21日に発表しました。

- ※1

短絡許容時間8マイクロ秒以上の1200V耐圧パワー半導体において。2017年9月22日現在(当社調べ)

短絡許容時間8マイクロ秒以上の1200V耐圧パワー半導体において。2017年9月22日現在(当社調べ) - ※2

Silicon Carbide(炭化ケイ素)

Silicon Carbide(炭化ケイ素)

開発の特長

- 独自構造により、高信頼性と省エネを両立

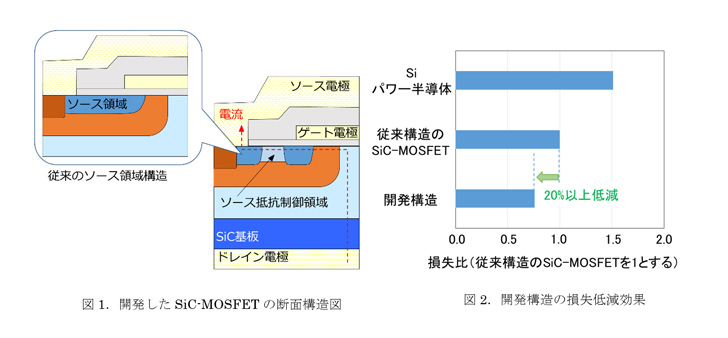

- ・通常、単一構造で構成するソース領域にソース抵抗制御領域を形成することにより、搭載機器の短絡発生時の電流を低減し、短絡許容時間を延ばして素子破壊を抑制(図1)

- ・従来構造のSiC-MOSFET※3に対し、同一短絡許容時間において、室温における素子のオン抵抗※4を40%低減し※5、20%以上電力の低損失化を実現(図2)

- ※3

Metal-Oxide-Semiconductor Field-Effect Transistor:金属酸化膜半導体電界効果トランジスター

Metal-Oxide-Semiconductor Field-Effect Transistor:金属酸化膜半導体電界効果トランジスター - ※4

パワー半導体素子の性能指数。素子面積と素子抵抗の積で表され、小型化・低抵抗化により小さくなる

パワー半導体素子の性能指数。素子面積と素子抵抗の積で表され、小型化・低抵抗化により小さくなる - ※5

当社従来構造の1200V耐圧SiC-MOSFETとの比較において

当社従来構造の1200V耐圧SiC-MOSFETとの比較において

- パワーエレクトロニクス機器への搭載時の回路設計負荷を軽減

- ・様々な耐圧のSiC-MOSFETに適用できるほか、Siパワー半導体ですでに確立されている短絡保護回路技術を併用することにより、短絡時の安全な保護動作を実現可能

今後の展開

今後、素子の信頼性とモジュールとしての評価を進め、2020年度以降の実用化を目指します。